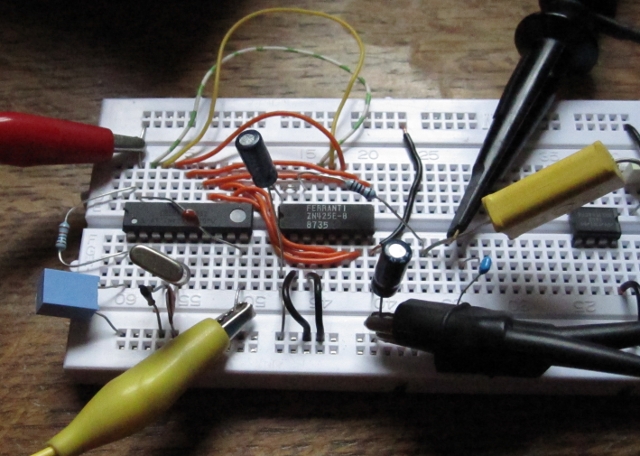

Heute wollte ich es wissen, ob die Idee von dk5pt mit einem ATtiny2313 umsetzbar ist.

/*

softdds ... a dds, implemented in software

based on an idea from dk5pt, December 2000

2011/11/12 OE1GCA

avr-gcc -Os -mmcu=attiny2313 softdds.c -o softdds

avr-objcopy -O ihex softdds softdds.hex

avrdude -c stk500v2 -pt2313 -P/dev/ttyUSB0 -U hfuse:w:0xdb:m -U lfuse:w:0xef:m

avrdude -c stk500v2 -pt2313 -P/dev/ttyUSB0 -U flash:w:softdds.hex

*/

#include <stdio.h>

#include <avr/io.h>

#include <avr/pgmspace.h>

/* Hardware connections */

/* ioport B: 8 bit DDS output */

const uint8_t sinustabelle[256] PROGMEM = {

127,130,133,136,139,143,146,149,152,155,158,161,164,167,170,173,

176,178,181,184,187,190,192,195,198,200,203,205,208,210,212,215,

217,219,221,223,225,227,229,231,233,234,236,238,239,240,242,243,

244,245,247,248,249,249,250,251,252,252,253,253,253,254,254,254,

254,254,254,254,253,253,253,252,252,251,250,249,249,248,247,245,

244,243,242,240,239,238,236,234,233,231,229,227,225,223,221,219,

217,215,212,210,208,205,203,200,198,195,192,190,187,184,181,178,

176,173,170,167,164,161,158,155,152,149,146,143,139,136,133,130,

127,124,121,118,115,111,108,105,102,99,96,93,90,87,84,81,

78,76,73,70,67,64,62,59,56,54,51,49,46,44,42,39,

37,35,33,31,29,27,25,23,21,20,18,16,15,14,12,11,

10,9,7,6,5,5,4,3,2,2,1,1,1,0,0,0,

0,0,0,0,1,1,1,2,2,3,4,5,5,6,7,9,

10,11,12,14,15,16,18,20,21,23,25,27,29,31,33,35,

37,39,42,44,46,49,51,54,56,59,62,64,67,70,73,76,

78,81,84,87,90,93,96,99,102,105,108,111,115,118,121,124};

int main (void){

uint32_t x=0; /* 24 bits phase accumulator */

/* *******************************************

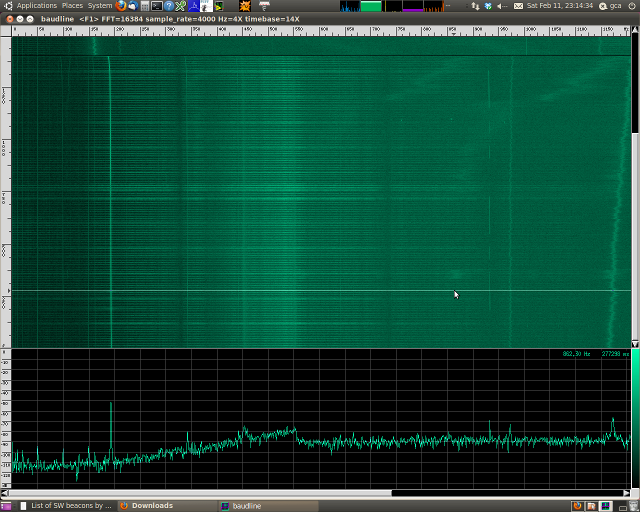

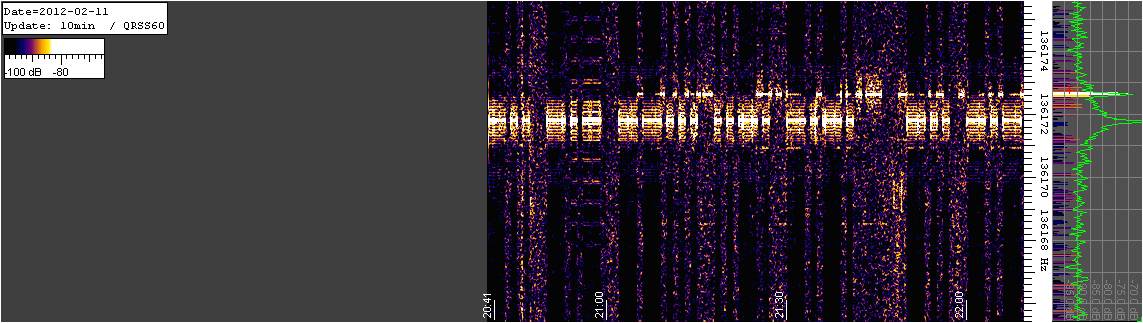

fclk = 847235Hz (14.403MHz / 17 cycles), phase accu 24 bit

m = fout / 1/2^24*fclk

fr = 1/2^24*fclk

*********************************************/

#define fxtl 14403300.0L /* crystal frequency */

#define fout 136175.0L /* desired output frequency */

#define bits 16777216UL /* 2^24 */

#define cycles 17UL /* current number of cycles */

#define fclk fxtl/cycles /* calculate phase accumulator clock */

#define m (uint32_t)((fout*bits)/(fxtl/cycles)) /* calculate phase increment value */

DDRB = 0xff; /* port B is output */

PORTB = 127;

while (1) {

x += m; /* add phase increment */

PORTB = pgm_read_byte (&sinustabelle[(uint8_t )((x>>16)&0xFF)]); /* ........ BBBBBBBB ........ ........ */

}

}

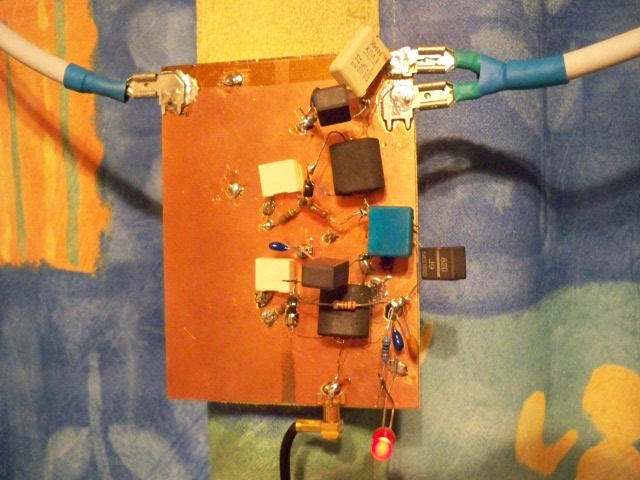

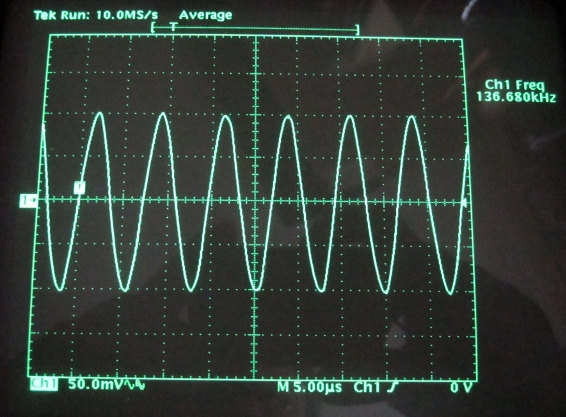

Als DAC verwende ich einen ZN425E8 und sogar mit einem RC Tiefpass schaut das Signal akzeptabel am Oszilloskop aus.

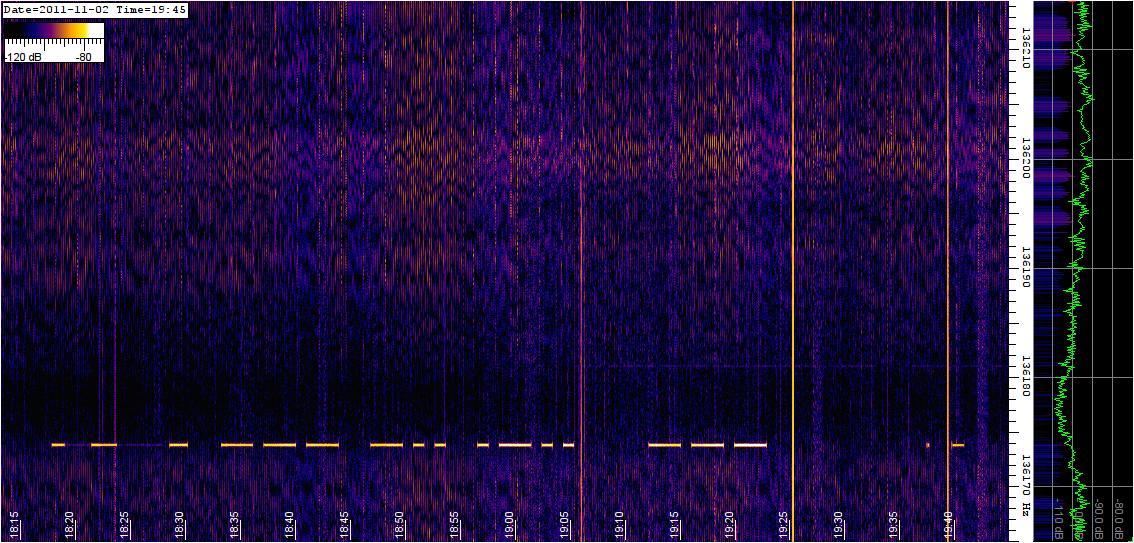

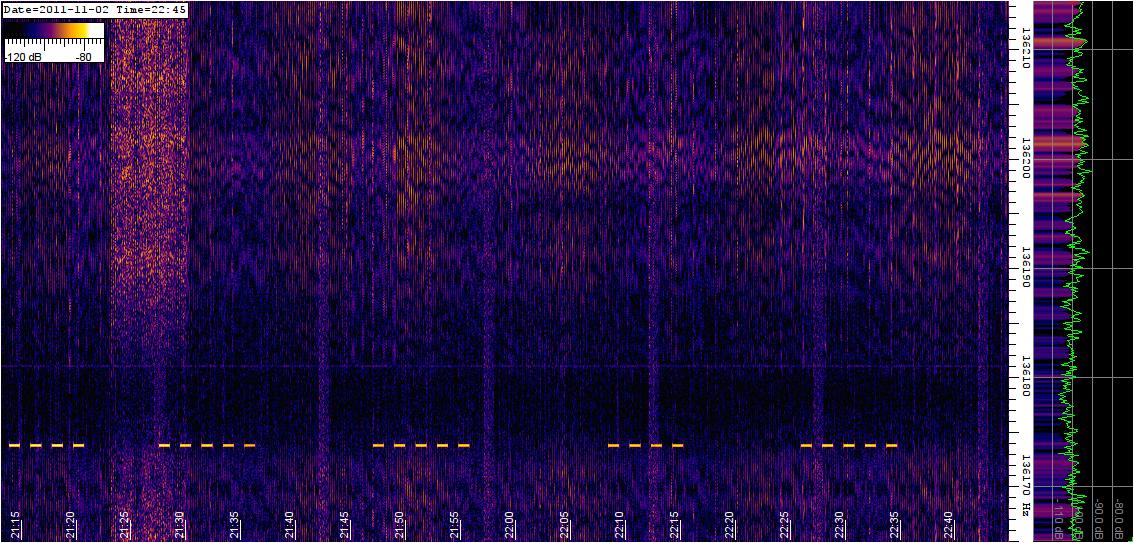

Der Kontrollempfänger (IC-R70) empfing einen schönen Pfeiton.

Jetzt muss man noch eine Interrupt-Routine für z.B.: Tasteneingaben für die Frequenz schreiben, dann hat man einen ultra-simplen Software-DDS.

![]()